Description

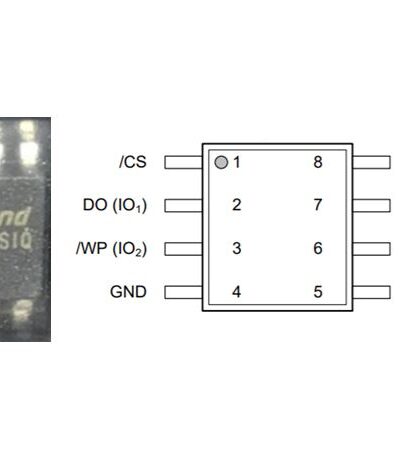

The FL-L family connects to a host system via a Serial Peripheral Interface (SPI). Traditional SPI single bit serial input and output (Single I/O or SIO) is supported as well as optional two bit (Dual I/O or DIO) and four bit wide Quad I/O (QIO) and Quad Peripheral Interface (QPI) commands. In addition, there are Double Data Rate (DDR) read commands for QIO and QPI that transfer address and read data on both edges of the clock.

The architecture features a Page Programming Buffer that allows up to 256-bytes to be programmed in one operation and provides individual 4KB sector, 32KB half block, 64KB block, or entire chip erase.

By using FL-L family devices at the higher clock rates supported, with Quad commands, the instruction read transfer rate can match or exceed traditional parallel interface, asynchronous, NOR Flash memories, while reducing signal count dramatically.

The FL-L family products offer high densities coupled with the flexibility and fast performance required by a variety of mobile or embedded applications. Provides an ideal storage solution for systems with limited space, signal connections, and power. These memories offer flexibility and performance well beyond ordinary serial flash devices. They are ideal for code shadowing to RAM, executing code directly (XIP), and storing re-programmable data.

Reviews

There are no reviews yet.